## CMOS SyncBiFIFO<sup>™</sup> WITH BUS-MATCHING AND BYTE SWAPPING 64 x 36 x 2

### **FEATURES:**

- Free-running CLKA and CLKB can be asynchronous or coincident (simultaneous reading and writing of data on a single clock edge is permitted)

- Two independent clocked FIFOs (64 x 36 storage capacity each) buffering data in opposite directions

- · Mailbox bypass Register for each FIFO

- Dynamic Port B bus sizing of 36 bits (long word), 18 bits (word), and 9 bits (byte)

- Selection of Big- or Little-Endian format for word and byte bus sizes

- · Three modes of byte-order swapping on port B

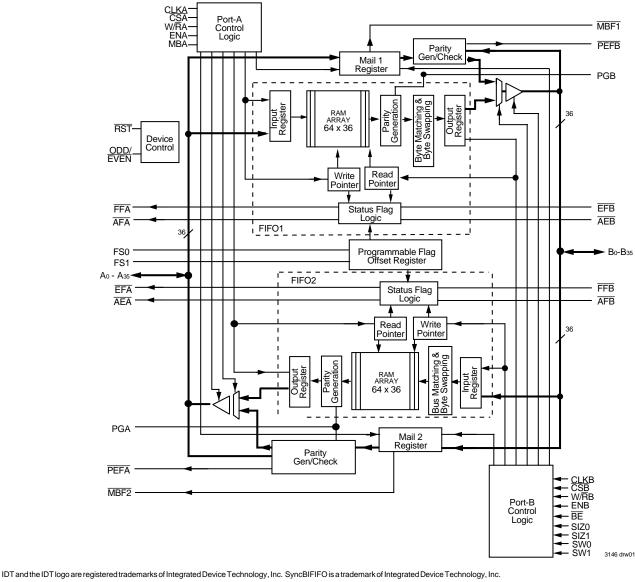

**FUNCTIONAL BLOCK DIAGRAM**

- Programmable Almost-Full and Almost-Empty flags

- Microprocessor interface control logic

- EFA, FFA, AEA, and AFA flags synchronized by CLKA

- EFB, FFB, AEB, and AFB flags synchronized by CLKB

- · Passive parity checking on each port

- · Parity generation can be selected for each port

- Supports clock frequencies up to 67 MHz

- Fast access times of 10 ns

- Available in 132-pin plastic quad flat package (PQF) or spacesaving 120-pin thin quad flat package (TQFP)

- Industrial temperature range (-40°C to +85°C) is available

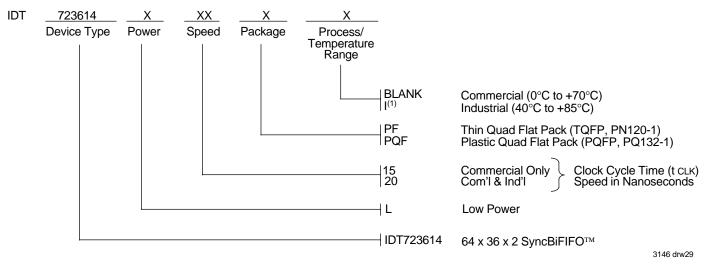

### COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

### **MARCH 2002**

#### COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

### **DESCRIPTION:**

The IDT723614 is a monolithic, high-speed, low-power CMOS bidirectional clocked FIFO memory. It supports clock frequencies up to 67MHz and has read access times as fast as 10ns. Two independent 64 x 36 dual-port SRAM FIFOs on board the chip buffer data in opposite directions. Each FIFO has flags to indicate empty and full conditions and two programmable flags (Almost-Full and Almost-Empty) to indicate when a selected number of words is stored in memory. FIFO data on port B can be input and output in 36-bit, 18-bit, and 9-bit formats

with a choice of big- or little-endian configurations. Three modes of byte-order swapping are possible with any bus size selection. Communication between each port can bypass the FIFOs via two 36-bit mailbox registers. Each mailbox register has a flag to signal when new mail has been stored. Parity is checked passively on each port and may be ignored if not desired. Parity generation can be selected for data read from each port. Two or more devices can be used in parallel to create wider data paths.

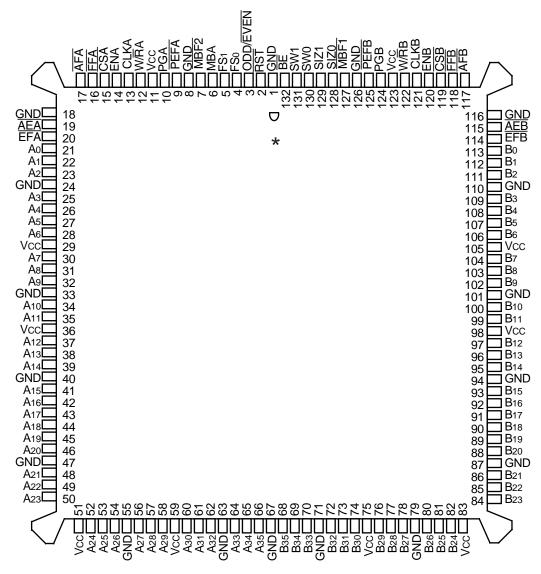

## **PIN CONFIGURATIONS**

\*Electrical pin 1 in center of beveled edge. Pin 1 identifier in corner.

3146 drw02

PQFP (PQ132-1, ORDER CODE: PQF) TOP VIEW

NOTES: 1. NC - No internal connection.

2. Uses Yamaichi socket IC51-1324-828.

#### COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

This device is a clocked FIFO, which means each port employs a synchronous interface. All data transfers through a port are gated to the LOW-to-HIGH transition of a continuous (free-running) port clock by enable signals. The clocks for each port are independent of one another and can be asynchronous or coincident. The enables for each port are arranged to provide a simple bidirectional interface between microprocessors and/or buses controlled by a synchronous interface. The Full Flag (FFA, FFB) and Almost-Full flag (ĀFA, ĀFB) of a FIFO are two-stage synchronized to the port clock that writes data to its array. The Empty Flag (EFA, EFB) and Almost-Empty (ĀEA, ĀEB) flag of a FIFO are two stage synchronized to the port clock that reads data from its array.

The IDT723614 is characterized for operation from 0°C to 70°C.

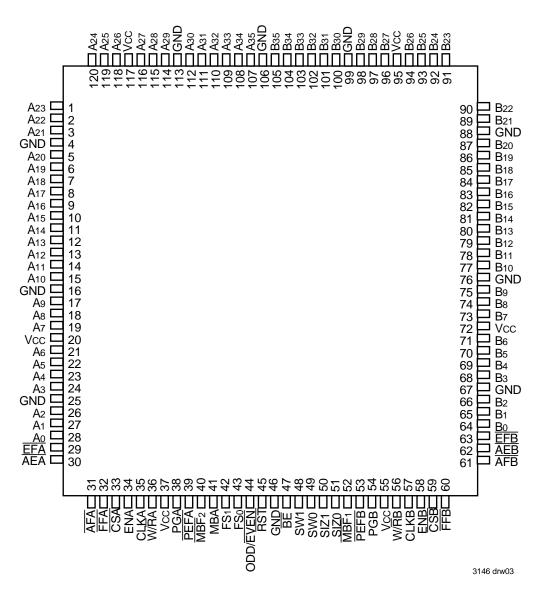

# **PIN CONFIGURATIONS (CONTINUED)**

TQFP (PN120-1, ORDER CODE: PF) TOP VIEW

3

# **PIN DESCRIPTION**

| Symbol   | Name                          | I/O           | Description                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|----------|-------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A0-A35   | Port A Data                   | I/O           | 36-bit bidirectional data port for side A.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| ĀĒĀ      | Port A Almost-Empty<br>Flag   | O<br>(Port A) | Programmable Almost-Empty flag synchronized to CLKA. It is LOW when the number of 36-bit words in FIFO2 is less than or equal to the value in the offset register, X.                                                                                                                                                                                                                          |  |  |  |

| AEB      | Port B Almost-Empty<br>Flag   | O<br>(Port B) | Programmable Almost-Empty flag synchronized to CLKB. It is LOW when the number of 36-bit words in FIFO1 is less than or equal to the value in the offset register, X.                                                                                                                                                                                                                          |  |  |  |

| ĀFĀ      | Port A Almost-Full<br>Flag    | O<br>(Port A) | Programmable Almost-Full flag synchronized to CLKA. It is LOW when the number of 36-bit empty locations in FIFO1 is less than or equal to the value in the offset register, X.                                                                                                                                                                                                                 |  |  |  |

| AFB      | Port B Almost-Full<br>Flag    | O<br>(Port B) | Programmable Almost-Full flag synchronized to CLKB. It is LOW when the number of 36-bit empty locations in FIFO2 is less than or equal to the value in the offset register, X.                                                                                                                                                                                                                 |  |  |  |

| B0-B35   | Port B Data                   | I/O           | 36-bit bidirectional data port for side B.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| BE       | Big-endian select             | I             | Selects the bytes on port B used during byte or word data transfer. A LOW on $\overline{\text{BE}}$ selects the most most significant bytes on B0-B35 for use, and a HIGH selects the least significant bytes.                                                                                                                                                                                 |  |  |  |

| CLKA     | Port A Clock                  | I             | CLKA is a continuous clock that synchronizes all data transfers through port A and can be asynchronous or coincident to CLKB. EFA, FFA, AFA, and AEA are synchronized to the LOW-to-HIGH transition of CLKA.                                                                                                                                                                                   |  |  |  |

| CLKB     | Port B Clock                  | I             | CLKB is a continuous clock that synchronizes all data transfers through port B and can be asynchronous or coincident to CLKA. Port B byte swapping and data port sizing operations are also synchronous to the LOW-to-HIGH transition of CLKB. EFB, FFB, AFB, and AEB are synchronized to the LOW-to-HIGH transition of CLKB.                                                                  |  |  |  |

| CSA      | Port A Chip Select            | I             | CSA must be LOW to enable a LOW-to-HIGH transition of CLKA to read or write data on port A.<br>The A0-A35 outputs are in the high-impedance state when CSA is HIGH.                                                                                                                                                                                                                            |  |  |  |

| CSB      | Port B Chip Select            | I             | CSB must be LOW to enable a LOW-to-HIGH transition of CLKB to read or write data on port B. The B0-B35 outputs are in the high-impedance state when CSB is HIGH.                                                                                                                                                                                                                               |  |  |  |

| ĒFĀ      | Port A Empty Flag             | O<br>(Port A) | <b>EFA</b> is synchronized to the LOW-to-HIGH transition of CLKA. When <b>EFA</b> is LOW, FIFO2 is empty, and reads from its memory are disabled. Data can be read from FIFO2 to the output register when <b>EFA</b> is HIGH. <b>EFA</b> is forced LOW when the device is reset and is set HIGH by the second LOW-to-HIGH transition of CLKA after data is loaded into empty FIFO2 memory.     |  |  |  |

| ĒFB      | Port B Empty Flag<br>(Port B) | 0             | <b>EFB</b> is synchronized to the LOW-to-HIGH transition of CLKB. When <b>EFB</b> is LOW, the FIFO1 is empty, and reads from its memory are disabled. Data can be read from FIFO1 to the output register when <b>EFB</b> is HIGH. <b>EFB</b> is forced LOW when the device is reset and is set HIGH by the second LOW-to-HIGH transition of CLKB after data is loaded into empty FIFO1 memory. |  |  |  |

| ENA      | Port A Enable                 | I             | ENA must be HIGH to enable a LOW-to-HIGH transition of CLKA to read or write data on port A.                                                                                                                                                                                                                                                                                                   |  |  |  |

| ENB      | Port B Enable                 | I             | ENB must be HIGH to enable a LOW-to-HIGH transition of CLKB to read or write data on port B.                                                                                                                                                                                                                                                                                                   |  |  |  |

| FFA      | Port A Full Flag              | O<br>(Port A) | FFA is synchronized to the LOW-to-HIGH transition of CLKA. When FFA is LOW, FIFO1 is full, and writes to its memory are disabled. FFA is forced LOW when the device is reset and is set HIGH by the second LOW-to-HIGH transition of CLKA after reset.                                                                                                                                         |  |  |  |

| FFB      | Port B Full Flag              | O<br>(Port B) | FFB is synchronized to the LOW-to-HIGH transition of CLKB. When FFB is LOW, FIFO2 is full, and writes to its memory are disabled. FFB is forced LOW when the device is reset and is set HIGH by the second LOW-to-HIGH transition of CLKB after reset.                                                                                                                                         |  |  |  |

| FS1, FS0 | Flag-Offset Selects           | I             | The LOW-to-HIGH transition of $\overline{RST}$ latches the values of FS0 and FS1, which selects one of four preset values for the Almost-Full flag and Almost-Empty flag offset.                                                                                                                                                                                                               |  |  |  |

| MBA      | Port A Mailbox<br>Select      | I             | A HIGH level on MBA chooses a mailbox register for a port A read or write operation. When the A0-A35 outputs are active, a HIGH level on MBA selects data from the mail2 register for output, and a LOW level selects FIFO2 output register data for output.                                                                                                                                   |  |  |  |

| MBF1     | Mail1 Register Flag           | 0             |                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

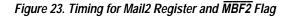

| MBF2     | Mail2 Register Flag           | 0             | MBF2 is set LOW by a LOW-to-HIGH transition of CLKB that writes data to the mail2 register.<br>Writes to the mail2 register are inhibited while MBF2 is set LOW. MBF2 is set HIGH by a LOW-to-<br>HIGH transition of CLKA when a port A read is selected and MBA is HIGH. MBF2 is set HIGH<br>when the device is reset.                                                                        |  |  |  |

# **PIN DESCRIPTION (CONTINUED)**

| Symbol       | Name                        | I/O           | Description                                                                                                                                                                                                                                                                                                                                                              |

|--------------|-----------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ODD/<br>EVEN | Odd/Even Parity<br>Select   | I             | Odd parity is checked on each port when ODD/EVEN is HIGH, and even parity is checked when ODD/EVEN is LOW. ODD/EVEN also selects the type of parity generated for each port if parity generation is enabled for a read operation.                                                                                                                                        |

| PEFA         | Port A Parity Error<br>Flag | O<br>(Port A) | When any byte applied to terminals A0-A35 fails parity, PEFA is LOW. Bytes are organized as A0-A8, A9-A17, A18-A26, and A27-A35, with the most significant bit of each byte serving as the parity bit. The type of parity checked is determined by the state of the ODD/EVEN input.                                                                                      |

|              |                             |               | The parity trees used to check the A0-A35 inputs are shared by the mail2 register to generate parity if parity generation is selected by PGA. Therefore, if a mail2 read parity generation is setup by having W/RA LOW, MBA HIGH, and PGA HIGH, the PEFA flag is forced HIGH regardless of the A0-A35 inputs.                                                            |

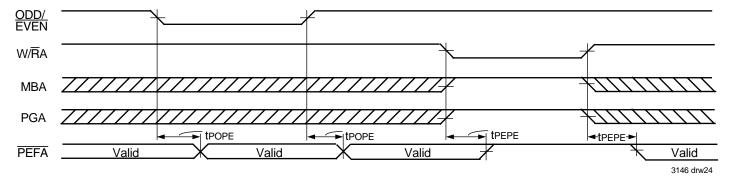

| PEFB         | Port B Parity Error<br>Flag | O<br>(Port B) | When any valid byte applied to terminals B0-B35 fails parity, PEFB is LOW. Bytes are organized as B0-B8, B9-B17, B18-B26, B27-B35 with the most significant bit of each byte serving as the parity bit. A byte is valid when it is used by the bus size selected for Port B. The type of parity checked is determined by the state of the ODD/EVEN input.                |

|              |                             |               | The parity trees used to check the B0-B35 inputs are shared by the mail 1 register to generate parity if parity generation is selected by PGB. Therefore, if a mail1 read with parity generation is setup by having W/RB LOW, SIZ1 and SIZ0 HIGH, and PGB HIGH, the PEFB flag is forced HIGH regardless of the state of the B0-B35 inputs.                               |

| PGA          | Port A Parity<br>Generation | I             | Parity is generated for data reads from port A when PGA is HIGH. The type of parity generated is selected by the state of the ODD/EVEN input. Bytes are organized as A0-A8, A9-A17, A18-A26, and A27-A35. The generated parity bits are output in the most significant bit of each byte.                                                                                 |

| PGB          | Port B Parity<br>Generation | I             | Parity is generated for data reads from port B when PGB is HIGH. The type of parity generated is selected by the state of the ODD/EVEN input. Bytes are organized as B0-B8, B9-B17, B18-B26, and B27-B35. The generated parity bits are output in the most significant bit of each byte.                                                                                 |

| RST          | Reset                       | I             | To reset the device, four LOW-to-HIGH transitions of CLKA and four LOW-to-HIGH transitions of CLKB must occur while RST is LOW. This sets the AFA, AFB, MBF1, and MBF2 flags HIGH and the EFA, EFB, AEA, AEB, FFA, and FFB flags LOW. The LOW-to-HIGH transition of RST latches the status of the FS1 and FS0 inputs to select Almost-Full and Almost-Emptyflag offsets. |

| SIZO, SIZ1   | Port B Bus Size<br>Selects  | l<br>(Port B) | A LOW-to-HIGH transition of CLKB latches the states of SIZ0, SIZ1, and $\overline{\text{BE}}$ , and the following LOW-to-HIGH transition of CLKB implements the latched states as a port B bus size. Port B bus sizes can be long word, word, or byte. A high on both SIZ0 and SIZ1 accesses the mailbox registers for a port B 36-bit write or read.                    |

| SW0, SW1     | Port B byte Swap<br>Select  | l<br>(Port B) | At the beginning of each long word transfer, one of four modes of byte-order swapping is selected by SW0 and SW1. The four modes are no swap, byte swap, word swap, and byte-word swap. Byte-order swapping is possible with any bus-size selection.                                                                                                                     |

| W/RA         | Port A Write/Read<br>Select | I             | A HIGH selects a write operation and a LOW selects a read operation on for a LOW-to-HIGH port A transition of CLKA. The A0-A35 outputs are in the high-impedance state when W/RA is HIGH.                                                                                                                                                                                |

| W/RB         | Port B Write/Read<br>Select | I             | A HIGH selects a write operation and a LOW selects a read operation on for a LOW-to-HIGH port B B transition of CLKB. The B0-B35 outputs are in the high-impedance state when $W/RB$ is HIGH.                                                                                                                                                                            |

# ABSOLUTE MAXIMUM RATINGS OVER OPERATING FREE-AIR TEMPERATURE RANGE (UNLESS OTHERWISE NOTED)<sup>(1)</sup>

| Symbol            | Rating                                     | Commercial      | Unit |

|-------------------|--------------------------------------------|-----------------|------|

| Vcc               | Supply Voltage Range                       | –0.5 to 7       | V    |

| VI <sup>(2)</sup> | Input Voltage Range                        | -0.5 to VCC+0.5 | V    |

| V0 <sup>(2)</sup> | Output Voltage Range                       | -0.5 to VCC+0.5 | V    |

| Ік                | Input Clamp Current, (VI < 0 or VI > Vcc)  | ±20             | mA   |

| Іок               | Output Clamp Current, (Vo < 0 or Vo > Vcc) | ±50             | mA   |

| Ιουτ              | Continuous Output Current, (Vo = 0 to Vcc) | ±50             | mA   |

| lcc               | Continuous Current Through Vcc or GND      | ±500            | mA   |

| Tstg              | Storage Temperature Range                  | -65 to 150      | °C   |

NOTES:

1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2. The input and output voltage ratings may be exceeded provided the input and output current ratings are observed.

# RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter                      | Min. | Max. | Unit |

|--------|--------------------------------|------|------|------|

| Vcc    | Supply Voltage                 | 4.5  | 5.5  | V    |

| Vih    | HIGH Level Input Voltage       | 2    | -    | V    |

| VIL    | LOW-Level Input Voltage        | -    | 0.8  | V    |

| Іон    | HIGH-Level Output Current      | -    | -4   | mA   |

| IOL    | LOW-Level Output Current       | -    | 8    | mA   |

| TA     | Operating Free-air Temperature | 0    | 70   | °C   |

# ELECTRICAL CHARACTERISTICS OVER RECOMMENDED OPERATING FREE-AIR TEMPERATURE RANGE (UNLESS OTHERWISE NOTED)

| Parameter          |              |               | Min.            | Тур.(1) | Max. | Unit |    |

|--------------------|--------------|---------------|-----------------|---------|------|------|----|

| Vон                | VCC = 4.5V,  | Iон = -4 mA   |                 | 2.4     |      |      | V  |

| Vol                | Vcc = 4.5 V, | Iol = 8 mA    |                 |         |      | 0.5  | V  |

| li                 | Vcc = 5.5 V, | VI = VCC or 0 |                 |         |      | ±50  | μA |

| loz                | Vcc = 5.5 V, | Vo = Vcc or 0 |                 |         |      | ±50  | μA |

| ICC <sup>(2)</sup> | Vcc = 5.5 V, | lo = 0 mA,    | VI = Vcc or GND |         |      | 1    | mA |

| Cin                | VI = 0,      | f = 1 MHz     |                 |         | 4    |      | pF |

| Соит               | Vo = 0,      | f = 1 MHZ     |                 |         | 8    |      | pF |

NOTES:

1. All typical values are at Vcc = 5 V, TA =  $25^{\circ}$ C.

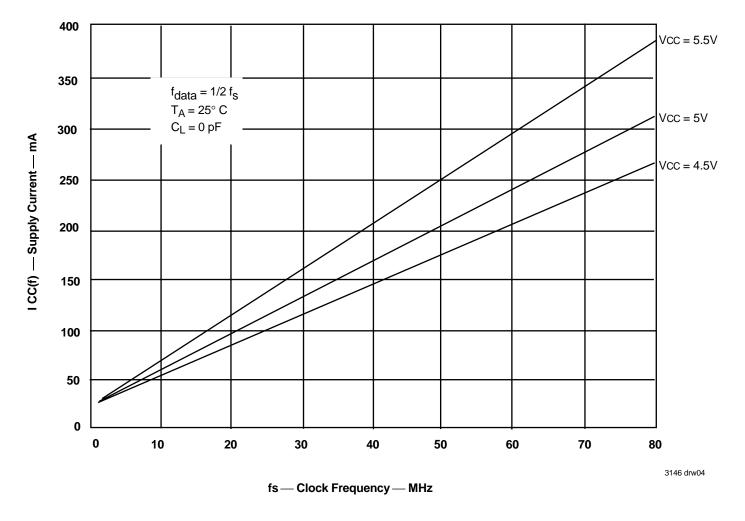

2. For additional ICC information, see the following page.

# **CALCULATING POWER DISSIPATION**

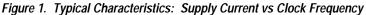

The Icc(f) current for the graph in Figure 1 was taken while simultaneously reading and writing the FIFO on the IDT723614 with CLKA and CLKB set to fs. All data inputs and data outputs change state during each clock cycle to consume the highest supply current. Data outputs were disconnected to normalize the graph to a zero-capacitance load. Once the capacitive lead per data-output channel is known, the power dissipation can be calculated with the equation below.

With ICC(f) taken from Figure 1, the maximum power dissipation (PT) of the IDT723614 can be calculated by:

$\begin{array}{rcl} \mathsf{PT} = \mathsf{VCc} \ x \ \mathsf{Icc}(\mathsf{f}) + \Sigma \left(\mathsf{CL} \ x \ \mathsf{VOH}^2 \ x \ \mathsf{fo}\right) \\ \text{where:} \\ \mathsf{CL} &= & \mathsf{output} \ \mathsf{capacitance} \ \mathsf{load} \\ \mathsf{fo} &= & \mathsf{switching} \ \mathsf{frequency} \ \mathsf{of} \ \mathsf{an} \ \mathsf{output} \\ \mathsf{VOH} &= & \mathsf{output} \ \mathsf{high} \ \mathsf{level} \ \mathsf{voltage} \end{array}$

When no reads or writes are occurring on the IDT723614, the power dissipated by a single clock (CLKA or CLKB) input running at frequency fs is calculated by:

7

PT=VCC x fs x 0.290 mA/MHz

# DC ELECTRICAL CHARACTERISTICS OVER RECOMMENDED RANGES OF SUPPLY VOLTAGE AND OPERATING FREE-AIR TEMPERATURE

(Commercial: Vcc =  $5.0V \pm 10\%$ , TA =  $0^{\circ}C$  to + $70^{\circ}C$ ; Industrial; Vcc =  $5.0V \pm 10\%$ , TA =  $40^{\circ}C$  to + $85^{\circ}C$ )

|                       |                                                                                                                                                              |        | ercial | Com'l 8 |      |      |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|---------|------|------|

|                       |                                                                                                                                                              | IDT723 | 614L15 | IDT723  |      |      |

| Symbol                | Parameter                                                                                                                                                    | Min.   | Max.   | Min.    | Max. | Unit |

| fS                    | Clock Frequency, CLKA or CLKB                                                                                                                                | -      | 66.7   | -       | 50   | MHz  |

| <b>t</b> CLK          | Clock Cycle Time, CLKA or CLKB                                                                                                                               | 15     | -      | 20      | -    | ns   |

| <b>t</b> CLKH         | Pulse Duration, CLKA and CLKB HIGH                                                                                                                           | 6      | -      | 8       | -    | ns   |

| <b>t</b> CLKL         | Pulse Duration, CLKA and CLKB LOW                                                                                                                            | 6      | _      | 8       | _    | ns   |

| tDS                   | Setup Time, A0-A35 before CLKA $\uparrow$ and B0-B35 before CLKB $\uparrow$                                                                                  | 4      | -      | 5       | _    | ns   |

| tens                  | Setup Time, CSA, W/RA, ENA and MBA before CLKA1; CSB, W/RB and ENB before CLKB1                                                                              | 5      | -      | 5       | _    | ns   |

| tszs                  | Setup Time, SIZ0, SIZ1, and $\overline{BE}$ before CLKB $\uparrow$                                                                                           | 4      | -      | 5       | -    | ns   |

| tsws                  | Setup Time, SW0 and SW1 before CLKB↑                                                                                                                         | 5      | -      | 7       | -    | ns   |

| tpgs                  | Setup Time, ODD/ $\overline{EVEN}$ and PGA before CLKA $\uparrow$ ; ODD/ $\overline{EVEN}$ and PGB before CLKB $\uparrow^{\scriptscriptstyle(2)}$            | 4      | -      | 5       | -    | ns   |

| trsts                 | Setup Time, $\overline{\text{RST}}$ LOW before CLKA $\uparrow$ or CLKB $\uparrow^{(3)}$                                                                      | 5      | -      | 6       | -    | ns   |

| tFSS                  | Setup Time, FS0 and FS1 before RST HIGH                                                                                                                      | 5      | -      | 6       | -    | ns   |

| tDH                   | Hold Time, A0-A35 after CLKA $\uparrow$ and B0-B35 after CLKB $\uparrow$                                                                                     | 1      | -      | 1       | -    | ns   |

| tenh                  | Hold Time, $\overline{CSA}$ , W/ $\overline{RA}$ , ENA and MBA after CLKA $\uparrow$ ; $\overline{CSB}$ , W/ $\overline{RB}$ , and ENB after CLKB $\uparrow$ | 1      | -      | 1       | -    | ns   |

| tszh                  | Hold Time, SIZ0, SIZ1, and BE after CLKB↑                                                                                                                    | 2      | -      | 2       | -    | ns   |

| tswn                  | Hold Time, SW0 and SW1 after CLKB↑                                                                                                                           | 0      | -      | 0       | -    | ns   |

| tpgh                  | Hold Time, ODD/ $\overline{\rm EVEN}$ and PGA after CLKA $\uparrow$ ; ODD/ $\overline{\rm EVEN}$ and PGB after CLKB $\uparrow^{\scriptscriptstyle (2)}$      | 0      | -      | 0       | -    | ns   |

| trsth                 | Hold Time, $\overline{\text{RST}}$ LOW after CLKA $\uparrow$ or CLKB $\uparrow^{(3)}$                                                                        | 5      | -      | 6       | -    | ns   |

| tfsh                  | Hold Time, FS0 and FS1 after RST HIGH                                                                                                                        | 4      | -      | 4       | _    | ns   |

| tskew1 <sup>(4)</sup> | Skew Time, between CLKA $\uparrow$ and CLKB $\uparrow$ for EFA, EFB, FFA, and FFB                                                                            | 8      | _      | 8       | -    | ns   |

| tskew2 <sup>(4)</sup> | Skew Time, between CLKA $\uparrow$ and CLKB $\uparrow$ for $\overline{AEA}$ , $\overline{AEB}$ , $\overline{AFA}$ , and $\overline{AFB}$                     | 14     | -      | 16      | -    | ns   |

NOTES:

1. Industrial temperature range product for 20ns speed grade is available as a standard device. All other speed grades are available by special order.

2. Only applies for a clock edge that does a FIFO read.

3. Requirement to count the clock edge as one of at least four needed to reset a FIFO.

4. Skew time is not a timing constraint for proper device operation and is only included to illustrate the timing relationship between CLKA cycle and CLKB cycle.

# SWITCHING CHARACTERISTICS OVER RECOMMENDED RANGES OF SUPPLY VOLTAGE AND OPERATING FREE-AIR TEMPERATURE, CL = 30PF

(Commercial: Vcc =  $5.0V \pm 10\%$ , TA =  $0^{\circ}$ C to + $70^{\circ}$ C; Industrial; Vcc =  $5.0V \pm 10\%$ , TA =  $40^{\circ}$ C to + $85^{\circ}$ C)

|                      |                                                                                                                                                                                               |        | ercial | Com'l a |       |      |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|---------|-------|------|

|                      |                                                                                                                                                                                               | IDT723 | 614L15 | IDT723  | ]     |      |

| Symbol               | Parameter                                                                                                                                                                                     | Min.   | Max.   | Min.    | Мах.  | Unit |

| tA                   | Access Time, CLKA $\uparrow$ to A0-A35 and CLKB $\uparrow$ to B0-B35                                                                                                                          | 2      | 10     | 2       | 12    | ns   |

| tWFF                 | Propagation Delay Time, CLKA $\uparrow$ to $\overline{FFA}$ and CLKB $\uparrow$ to $\overline{FFB}$                                                                                           | 2      | 10     | 2       | 12    | ns   |

| tref                 | Propagation Delay Time, CLKA $\uparrow$ to $\overline{\text{EFA}}$ and CLKB $\uparrow$ to $\overline{\text{EFB}}$                                                                             | 2      | 10     | 2       | 12    | ns   |

| <b>t</b> PAE         | Propagation Delay Time, CLKA $\uparrow$ to $\overline{AEA}$ and CLKB $\uparrow$ to $\overline{AEB}$                                                                                           | 2      | 10     | 2       | 12    | ns   |

| tPAF                 | Propagation Delay Time, CLKA $\uparrow$ to $\overline{AFA}$ and CLKB $\uparrow$ to $\overline{AFB}$                                                                                           | 2      | 10     | 2       | 12    | ns   |

| <b>t</b> PMF         | Propagation Delay Time, CLKA $\uparrow$ to $\overline{\text{MBF1}}$ LOW or $\overline{\text{MBF2}}$ HIGH and CLKB $\uparrow$ to $\overline{\text{MBF2}}$ LOW or $\overline{\text{MBF1}}$ HIGH | 1      | 9      | 1       | 12    | ns   |

| <b>t</b> PMR         | Propagation Delay Time, CLKA $\uparrow$ to B0-B35 $^{\scriptscriptstyle (2)}$ and CLKB $\uparrow$ to A0-A35 $^{\scriptscriptstyle (3)}$                                                       | 3      | 11     | 3       | 13    | ns   |

| tppe <sup>(4)</sup>  | Propagation delay time, CLKB↑ to PEFB                                                                                                                                                         | 2      | 11     | 2       | 12    | ns   |

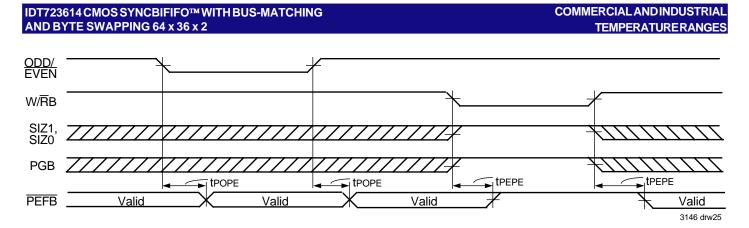

| tMDV                 | Propagation Delay Time, MBA to A0-A35 valid and SIZ1, SIZ0 to B0-B35 valid                                                                                                                    | 1      | 11     | 1       | 11. 5 | ns   |

| <b>t</b> PDPE        | Propagation Delay Time, A0-A35 valid to $\overline{PEFA}$ valid; B0-B35 valid to $\overline{PEFB}$ valid                                                                                      | 3      | 10     | 3       | 11    | ns   |

| <b>t</b> POPE        | Propagation Delay Time, ODD/EVEN to PEFA and PEFB                                                                                                                                             | 3      | 11     | 3       | 12    | ns   |

| tpopb <sup>(5)</sup> | Propagation Delay Time, ODD/EVEN to parity bits (A8, A17, A26, A35) and (B8, B17, B26, B35)                                                                                                   | 2      | 11     | 2       | 12    | ns   |

| tPEPE                | Propagation Delay Time, CSA, ENA, W/RA, MBA, or PGA to PEFA; CSB, ENB, W/RB, SIZ1, SIZ0, or PGB to PEFB                                                                                       | 1      | 11     | 1       | 12    | ns   |

| tpepb <sup>(5)</sup> | Propagation Delay Time, CSA, ENA, W/RA, MBA, or PGA to parity bits (A8, A17, A26, A35); CSB, ENB, W/RB, SIZ1, SIZ0, or PGB to parity bits (B8, B17, B26, B35)                                 | 3      | 12     | 3       | 13    | ns   |

| trsf                 | Propagation Delay Time, RST to (MBF1, MBF2) HIGH                                                                                                                                              | 1      | 15     | 1       | 20    | ns   |

| ten                  | Enable Time, $\overline{CSA}$ and W/RA LOW to A0-A35 active and $\overline{CSB}$ LOW and W/RB HIGH to B0-B35 active                                                                           | 2      | 10     | 2       | 12    | ns   |

| tdis                 | Disable Time, $\overline{CSA}$ or W/RA HIGH to A0-A35 at high-impedance and $\overline{CSB}$ HIGH or W/RB LOW to B0-B35 at high-impedance                                                     | 1      | 8      | 1       | 9     | ns   |

NOTES:

1. Industrial temperature range product for 20ns speed grade is available as a standard device. All other speed grades are available by special order.

2. Writing data to the mail1 register when the B0-B35 outputs are active and SIZ1, SIZ0 are HIGH.

3. Writing data to the mail2 register when the A0-A35 outputs are active and MBA is HIGH.

4. Only applies when a new port B bus size is implemented by the rising CLKB edge.

5. Only applies when reading data from a mail register.

### **SIGNAL DESCRIPTIONS**

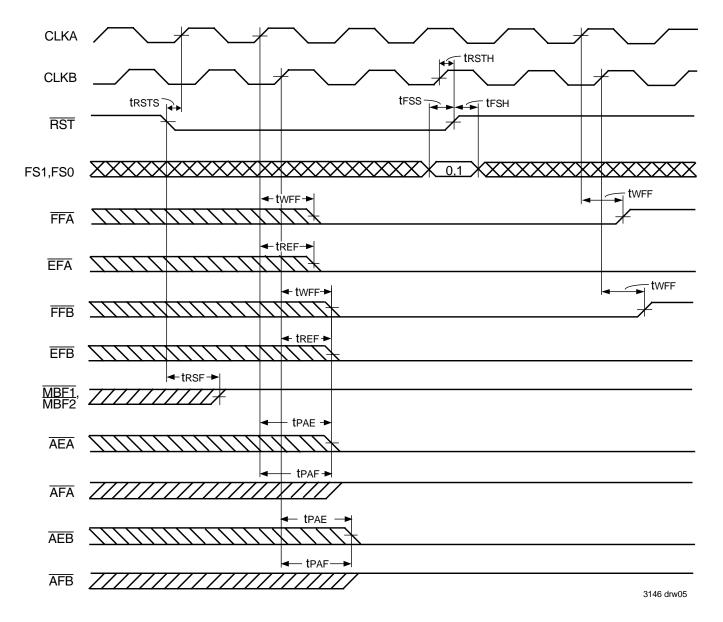

#### RESET

The IDT723614 is reset by taking the Reset (RST) input LOW for at least four port A clock (CLKA) and four port B clock (CLKB) LOW-to-HIGH transitions. The Reset input can switch asynchronously to the clocks. A device reset initializes the internal read and write pointers of each FIFO and forces the Full Flags (FFA, FFB) LOW, the Empty Flags (EFA, EFB) LOW, the Almost-Empty flags (AEA, AEB) LOW and the Almost-Full flags (AFA, AFB) HIGH. A reset also forces the Mailbox Flags (MBF1, MBF2) HIGH. After a reset, FFA is set HIGH after two LOW-to-HIGH transitions of CLKA and FFB is set HIGH after two LOW-to-HIGH transitions of CLKB. The device must be reset after power up before data is written to its memory.

A LOW-to-HIGH transition on the  $\overline{RST}$  input loads the Almost-Full and Almost-Empty Offset register (X) with the values selected by the Flag Select (FS0, FS1) inputs. The values that can be loaded into the registers are shown in Table 1.

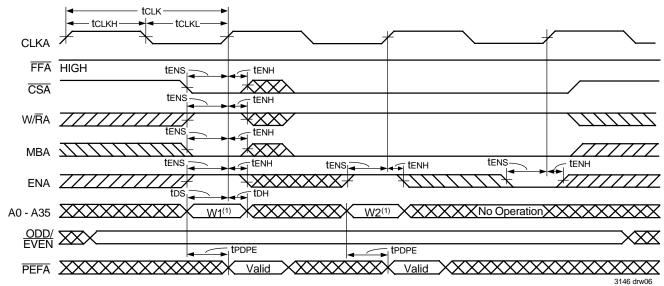

#### **FIFO WRITE/READ OPERATION**

The state of port A data A0-A35 outputs is controlled by the port A Chip Select (CSA) and the port A Write/Read select (W/RA). The A0-A35 outputs are in the high-impedance state when either CSA or W/RA is HIGH. The A0-A35 outputs are active when both CSA and W/RA are LOW. Data is loaded into FIFO1 from the A0-A35 inputs on a LOW-to-HIGH transition of CLKA when CSA is LOW, W/RA is HIGH, ENA is HIGH, MBA is LOW, and FFA is HIGH. Data is read from FIFO2 to the A0-A35 outputs by a LOW-to-HIGH transition of CLKA when CSA is LOW, W/RA is LOW, ENA is HIGH, MBA is LOW, and EFA is HIGH (see Table 2).

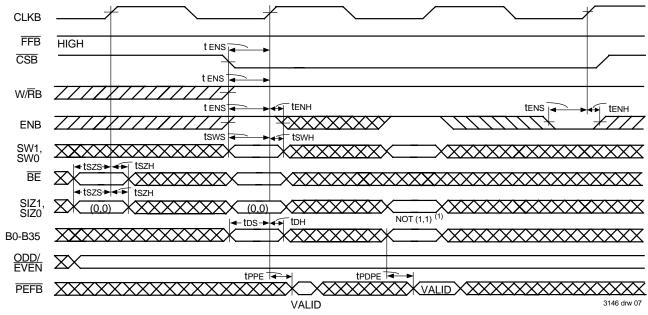

The port B control signals are identical to those of port A. The state of the port B data (B0-B35) outputs is controlled by the port B Chip Select ( $\overline{CSB}$ ) and the port B Write/Read select ( $W/\overline{R}B$ ). The B0-B35 outputs are in the high-impedance state when either  $\overline{CSB}$  or  $W/\overline{R}B$  is HIGH. The B0-B35 outputs are active when both  $\overline{CSB}$  and  $W/\overline{R}B$  are LOW. Data is loaded into FIFO2 from the B0-B35 inputs on a LOW-to-HIGH transition of CLKB when  $\overline{CSB}$  is LOW,  $W/\overline{R}B$  is HIGH, ENB is HIGH,  $\overline{EFB}$  is HIGH, and either SIZ0 or SIZ1 is LOW. Data isread from FIFO1 to the B0-B35 outputs by a LOW-to-HIGH transition of CLKB when  $\overline{CSB}$  is LOW,  $W/\overline{R}B$  is LOW,  $W/\overline{R}B$  is LOW,  $\overline{CSB}$  is LOW,  $W/\overline{R}B$  is LOW,  $\overline{CSB}$  is LOW,  $\overline{CSB}$  is LOW. Data isread from FIFO1 to the B0-B35 outputs by a LOW-to-HIGH transition of CLKB when  $\overline{CSB}$  is LOW,  $W/\overline{R}B$  is LOW,  $\overline{CSB}$  is LOW,  $\overline{CSB}$  is LOW,  $\overline{CSB}$  is LOW,  $\overline{CSB}$  is LOW. The B0-B35 outputs by a LOW-to-HIGH transition of CLKB when  $\overline{CSB}$  is LOW,  $W/\overline{R}B$  is LOW,  $\overline{CSB}$  is LOW,  $W/\overline{R}B$  is LOW,  $\overline{CSB}$  is LOW (see Table 3).

The setup and hold time constraints to the port clocks for the port Chip Selects (CSA, CSB) and Write/Read selects (W/RA, W/RB) are only for enabling write and read operations and are not related to high-impedance control of the data outputs. If a port enable is LOW during a clock cycle, the port Chip Select and Write/Read select can change states during the setup and hold time window of the cycle.

#### SYNCHRONIZED FIFO FLAGS

Each FIFO is synchronized to its port clock through two flip-flop stages. This is done to improve flag reliability by reducing the probability of metastable events on the output when CLKA and CLKB operate asynchronously to one another. EFA, AEA, FFA, and AFA are synchronized to CLKA. EFB, AEB, FFB, and AFB are synchronized to CLKB. Tables 4 and 5 show the relationship of each port flag to FIFO1 and FIFO2.

#### EMPTY FLAGS (EFA, EFB)

The Empty Flag of a FIFO is synchronized to the port clock that reads data from its array. When the Empty Flag is HIGH, new data can be read to the FIFO output register. When the Empty Flag is LOW, the FIFO is empty and attempted FIFO reads are ignored. When reading FIFO1 with a byte or word size on port

B, EFB is set LOW when the fourth byte or second word of the last long word is read.

The read pointer of a FIFO is incremented each time a new word is clocked to the output register. The state machine that controls an Empty Flag monitors a write-pointer and read-pointer comparator that indicates when the FIFO SRAM status is empty, empty+1, or empty+2. A word written to a FIFO can be read to the FIFO output register in a minimum of three cycles of the Empty Flag synchronizing clock. Therefore, an Empty Flag is LOW if a word in memory is the next data to be sent to the FIFO output register and two cycles of the port clock that reads data from the FIFO have not elapsed since the time the word was written. The Empty Flag of the FIFO is set HIGH by the second LOW-to-HIGH transition of the synchronizing clock, and the new data word can be read to the FIFO output register in the following cycle.

A LOW-to-HIGH transition on an Empty Flag synchronizing clock begins the first synchronization cycle of a write if the clock transition occurs at time tSKEW1 or greater after the write. Otherwise, the subsequent clock cycle can be the first synchronization cycle (see Figure 14 and 15).

#### FULL FLAG (FFA, FFB)

The Full Flag of a FIFO is synchronized to the port clock that writes data to its array. When the Full Flag is HIGH, a memory location is free in the SRAM to receive new data. No memory locations are free when the full flag is LOW and attempted writes to the FIFO are ignored.

Each time a word is written to a FIFO, the write pointer is incremented. The state machine that controls a Full Flag monitors a write-pointer and read-pointer comparator that indicates when the FIFO SRAM status is full, full-1, or full-2. From the time a word is read from a FIFO, the previous memory location is ready to be written in a minimum of three cycles of the Full Flag synchronizing clock. Therefore, a Full Flag is LOW if less than two cycles of the Full Flag synchronizing clock have elapsed since the next memory write location has been read. The second LOW-to-HIGH transition on the Full Flag synchronization clock after the read sets the Full Flag HIGH and the data can be written in the following clock cycle.

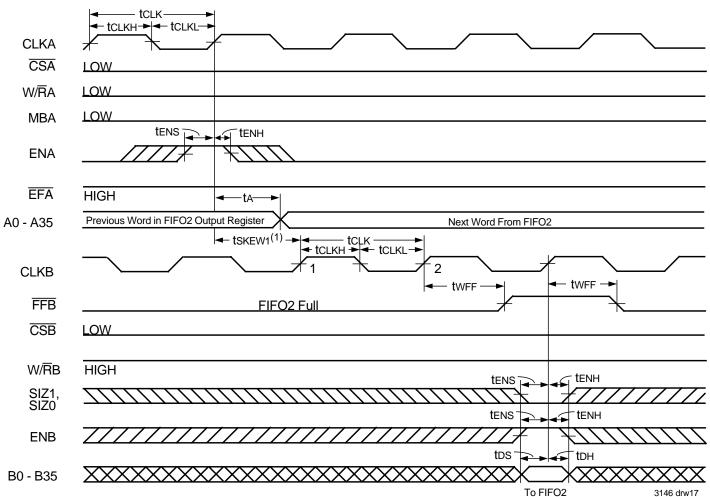

A LOW-to-HIGH transition on a Full Flag synchronizing clock begins the first synchronization cycle of a read if the clock transition occurs at time tskew1 or greater after the read. Otherwise, the subsequent clock cycle can be the first synchronization cycle (see Figure 16 and 17).

#### ALMOST-EMPTY FLAGS (AEA, AEB)

The Almost-Empty flag of a FIFO is synchronized to the port clock that reads data from its array. The state machine that controls an Almost-Empty flag monitors a write-pointer and a read-pointer comparator that indicates when the FIFO SRAM status is almost-empty, almost-empty+1, or almost-empty+2. The almost-empty state is defined by the value of the Almost-Full and Almost-Empty Offset register (X). This register is loaded with one of four preset values during a device reset (see Reset above). An Almost-Empty flag is LOW when the FIFO contains X or less long words in memory and is HIGH when the FIFO contains (X+1) or more long words.

Two LOW-to-HIGH transitions of the Almost-Empty flag synchronizing clock are required after a FIFO write for the Almost-Empty flag to reflect the new level of fill. Therefore, the Almost-Empty flag of a FIFO containing (X+1) or more long words remains LOW if two cycles of the synchronizing clock have not elapsed since the write that filled the memory to the (X+1) level. An Almost-Empty flag is set HIGH by the second LOW-to-HIGH transition of the synchronizing clock after the FIFO write that fills memory to the (X+1) level. A LOW-to-HIGH transition of an Almost-Empty flag synchronizing clock begins the first synchronization cycle if it occurs at time

tskew2 or greater after the write that fills the FIFO to (X+1) long words. Otherwise, the subsequent synchronizing clock cycle can be the first synchronization cycle (see Figure 18 and 19).

#### ALMOST FULL FLAGS (AFA, AFB)

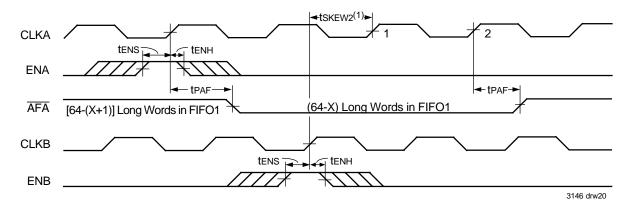

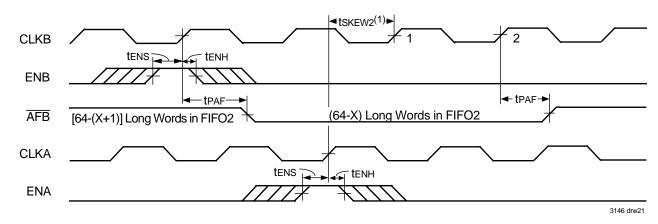

The Almost-Full flag of a FIFO is synchronized to the port clock that writes data to its array. The state machine that controls an Almost-Full flag monitors a write-pointer and read-pointer comparator that indicates when the FIFO SRAM status is almost full, almost full-1, or almost full-2. The almost-full state is defined by the value of the Almost-Full and Almost-Empty Offset register (X). This register is loaded with one of four preset values during a device reset (see Reset above). An Almost-Full flag is LOW when the FIFO contains (64-X) or more long words in memory and is HIGH when the FIFO contains [64-(X+1)] or less long words.

Two LOW-to-HIGH transitions of the Almost-Full flag synchronizing clock are required after a FIFO read for the Almost-Full flag to reflect the new level

### **TABLE 1 — FLAG PROGRAMMING**

| FS1 | FS0 | RST        | ALMOST-FULL AND<br>ALMOST-EMPTY FLAG<br>OFFSET REGISTER (X) |

|-----|-----|------------|-------------------------------------------------------------|

| Н   | Н   | $\uparrow$ | 16                                                          |

| Н   | L   | $\uparrow$ | 12                                                          |

| L   | Н   | $\uparrow$ | 8                                                           |

| L   | L   | $\uparrow$ | 4                                                           |

of fill. Therefore, the Almost-Full flag of a FIFO containing [64-(X+1)] or less words remains LOW if two cycles of the synchronizing clock have not elapsed since the read that reduced the number of long words in memory to [64-(X+1)]. An Almost-Full flag is set HIGH by the second LOW-to-HIGH transition of the synchronizing clock after the FIFO read that reduces the number of long words in memory to [64-(X+1)]. A LOW-to-HIGH transition of an Almost-Full flag synchronizing clock begins the first synchronization cycle if it occurs at time tsKEW2 or greater after the read that reduces the number of long words in memory to [64-(X+1)]. Otherwise, the subsequent synchronizing clock cycle can be the first synchronization cycle (see Figure 20 and 21).

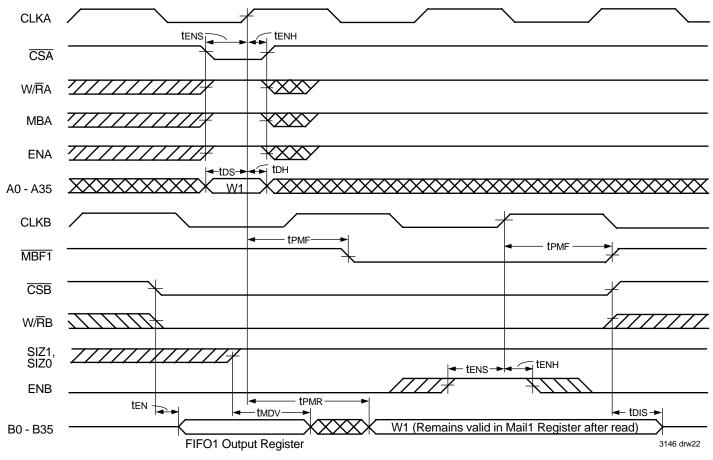

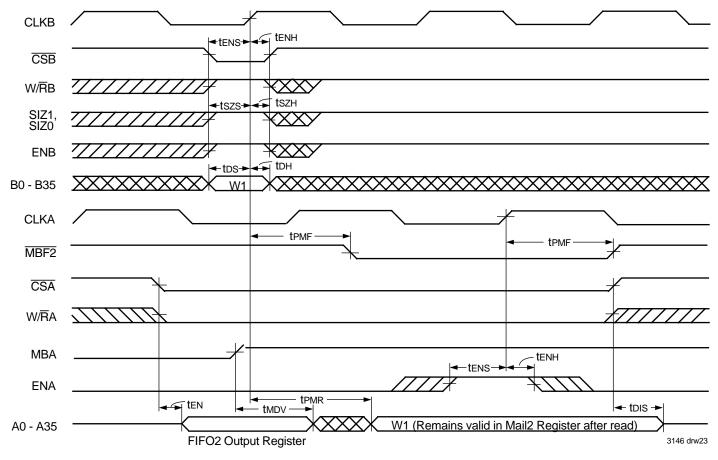

#### MAILBOX REGISTERS

Each FIFO has a 36-bit bypass register to pass command and control information between port A and port B without putting it in queue. The Mailbox-Select (MBA, MBB) inputs choose between a mail register and a FIFO for a port data transfer operation. A LOW-to-HIGH transition on CLKA writes A0-A35 data to the mail1 register when a port A write is selected by CSA, W/RA, and ENA with MBA HIGH. A LOW-to-HIGH transition on CLKB writes B0-B35 data to the mail2 register when a port B write is selected by CSB, W/RB, and ENB with both SIZ1 and SIZ0 HIGH. Writing data to a mail register sets the corresponding flag (MBF1 or MBF2) LOW. Attempted writes to a mail register are ignored while the mail flag is LOW.

When the port A data outputs (A0-A35) are active, the data on the bus comes from the FIFO2 output register when MBA is LOW and from the mail2 register when MBA is HIGH. When the port B data outputs (B0-B35) are active, the data on the bus comes from the FIFO1 output register when either one or both SIZ1 and SIZ0 are LOW and from the mail2 register when both SIZ1 and SIZ0 are HIGH. The Mail1 Register Flag (MBF1) is set HIGH

# TABLE 2 — PORT-A ENABLE FUNCTION TABLE

| <b>C</b> SA | W/RA | ENA | MBA | CLKA       | A0-A35 Outputs                | Port Functions             |

|-------------|------|-----|-----|------------|-------------------------------|----------------------------|

| Н           | Х    | Х   | Х   | Х          | In High-Impedance State       | None                       |

| L           | Н    | L   | Х   | Х          | In High-Impedance State       | None                       |

| L           | Н    | Н   | L   | $\uparrow$ | In High-Impedance State       | FIFO1 Write                |

| L           | Н    | Н   | Н   | $\uparrow$ | In High-Impedance State       | Mail1 Write                |

| L           | L    | L   | L   | Х          | Active, FIFO2 Output Register | None                       |

| L           | L    | Н   | L   | $\uparrow$ | Active, FIFO2 Output Register | FIFO2 Read                 |

| L           | L    | L   | Н   | Х          | Active, Mail2 Register        | None                       |

| L           | L    | Н   | Н   | $\uparrow$ | Active, Mail2 Register        | Mail2 Read (Set MBF2 HIGH) |

### TABLE 3 — PORT-B ENABLE FUNCTION TABLE

| <b>C</b> SB | W/RB | ENB | SIZ1, SIZ0    | CLKB       | B0-B35 Outputs                | Port Functions             |

|-------------|------|-----|---------------|------------|-------------------------------|----------------------------|

| Н           | Х    | Х   | Х             | Х          | In High-Impedance State       | None                       |

| L           | Н    | L   | Х             | Х          | In High-Impedance State       | None                       |

| L           | Н    | Н   | One, both LOW | $\uparrow$ | In High-Impedance State       | FIFO2 Write                |

| L           | Н    | Н   | Both HIGH     | $\uparrow$ | In High-Impedance State       | Mail2 Write                |

| L           | L    | L   | One, both LOW | Х          | Active, FIFO1 Output Register | None                       |

| L           | L    | Н   | One, both LOW | $\uparrow$ | Active, FIFO1 Output Register | FIFO1 read                 |

| L           | L    | L   | Both HIGH     | Х          | Active, Mail1 Register        | None                       |

| L           | L    | Н   | Both HIGH     | $\uparrow$ | Active, Mail1 Register        | Mail1 Read (Set MBF1 HIGH) |

by a rising CLKB edge when a port Bread is selected by CSB, W/RB, and ENB with both SIZ1 and SIZ0 HIGH. The Mail2 Register Flag (MBF2) is set HIGH by a LOW-to-HIGH transition on CLKA when port A read is selected by CSA, W/RA, and ENA and MBA is HIGH. The data in the mail register remains intact after it is read and changes only when new data is written to the register.

| Number of 36-Bit<br>Words in the FIFO1 <sup>(1)</sup> | Synchronized<br>to CLKB |     | Synchronized<br>to CLKA |     |

|-------------------------------------------------------|-------------------------|-----|-------------------------|-----|

|                                                       | EFB                     | AEB | ĀFĀ                     | FFA |

| 0                                                     | L                       | L   | Н                       | Н   |

| 1 to X                                                | Н                       | L   | Н                       | Н   |

| (X+1) to [64-(X+1)]                                   | Н                       | Н   | Н                       | Н   |

| (64-X) to 63                                          | Н                       | Н   | L                       | Н   |

| 64                                                    | Н                       | Н   | L                       | L   |

### **TABLE 4 — FIFO1 FLAG OPERATION**

### **TABLE 5 — FIFO2 FLAG OPERATION**

| Number of 36-Bit<br>Words in the FIFO2 <sup>(1)</sup> |     | ronized<br>SLKA | Synchronized<br>to CLKB |     |  |

|-------------------------------------------------------|-----|-----------------|-------------------------|-----|--|

|                                                       | ĒFĀ | ĀĒĀ             | AFB                     | FFB |  |

| 0                                                     | L   | L               | Н                       | Н   |  |

| 1 to X                                                | Н   | L               | Н                       | Н   |  |

| (X+1) to [64-(X+1)]                                   | Н   | Н               | Н                       | Н   |  |

| (64-X) to 63                                          | Н   | Н               | L                       | Н   |  |

| 64                                                    | Н   | Н               | L                       | L   |  |

NOTE:

1. X is the value in the Almost-Empty flag and Almost-Full flag Offset register.

#### DYNAMIC BUS SIZING

The port B bus can be configured in a 36-bit long word, 18-bit word, or 9bit byte format for data read from FIFO1 or written to FIFO2. Word- and bytesize bus selections can utilize the most significant bytes of the bus (Big-Endian) or least significant bytes of the bus (Little-Endian). Port B bus size can be changed dynamically and synchronous to CLKB to communicate with peripherals of various bus widths.

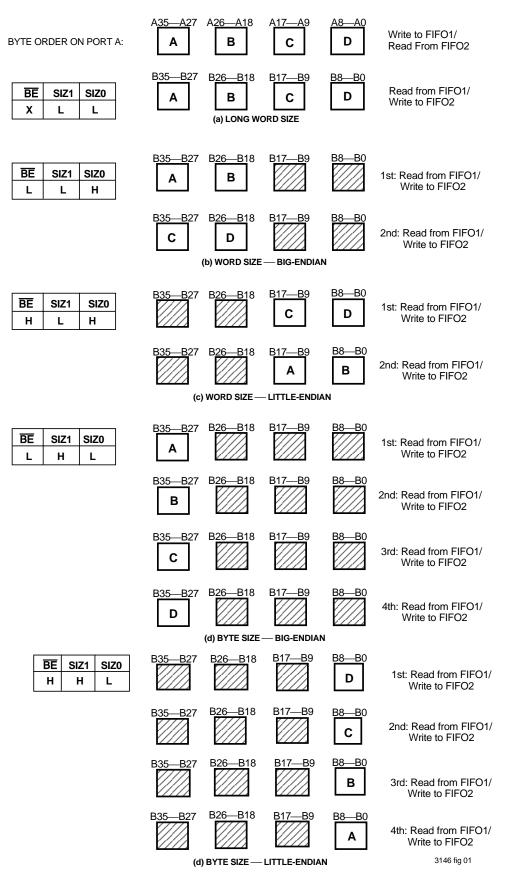

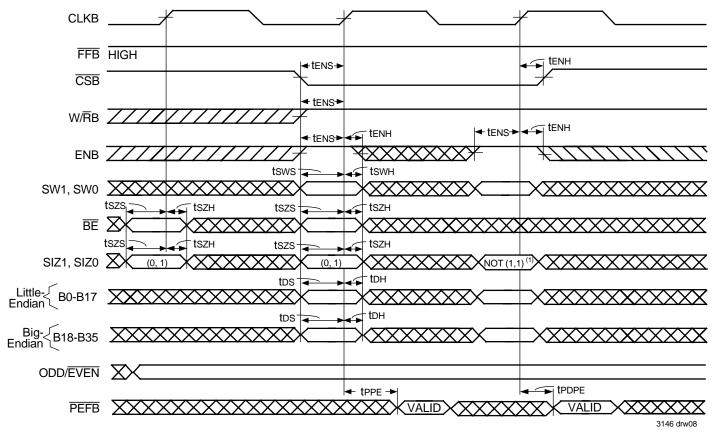

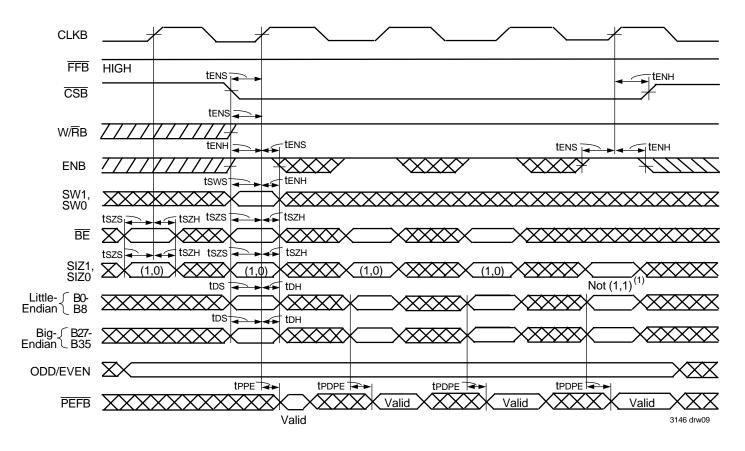

The levels applied to the port B bus Size select (SIZ0, SIZ1) inputs and the Big-Endian select ( $\overline{BE}$ ) input are stored on each CLKB LOW-to-HIGH transition. The stored port B bus size selection is implemented by the next rising edge on CLKB according to Figure 2.

Only 36-bit long-word data is written to or read from the two FIFO memories on the IDT723614. Bus-matching operations are done after data is read from the FIFO1 RAM and before data is written to the FIFO2 RAM. Port B bus sizing does not apply to mail register operations.

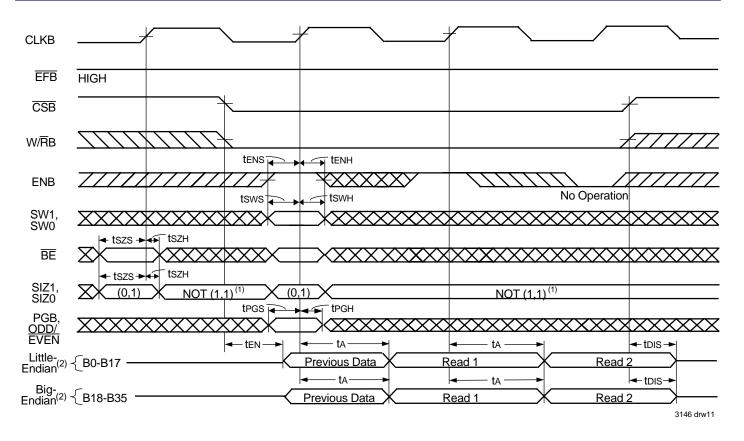

#### **BUS-MATCHING FIFO1 READS**

Data is read from the FIFO1 RAM in 36-bit long word increments. If a long word bus size is implemented, the entire long word immediately shifts to the FIFO1 output register. If byte or word size is implemented on port B, only the first one or two bytes appear on the selected portion of the FIFO1 output register, with the rest of the long word stored in auxiliary registers. In this case,

subsequent FIFO1 reads with the same bus-size implementation output the rest of the long word to the FIFO1 output register in the order shown by Figure 2.

Each FIFO1 read with a new bus-size implementation automatically unloads data from the FIFO1 RAM to its output register and auxiliary registers. Therefore, implementing a new port B bus size and performing a FIFO1 read before all bytes or words stored in the auxiliary registers have been read results in a loss of the unread long word data.

When reading data from FIFO1 in byte or word format, the unused B0-B35 outputs remain inactive but static, with the unused FIFO1 output register bits holding the last data value to decrease power consumption.

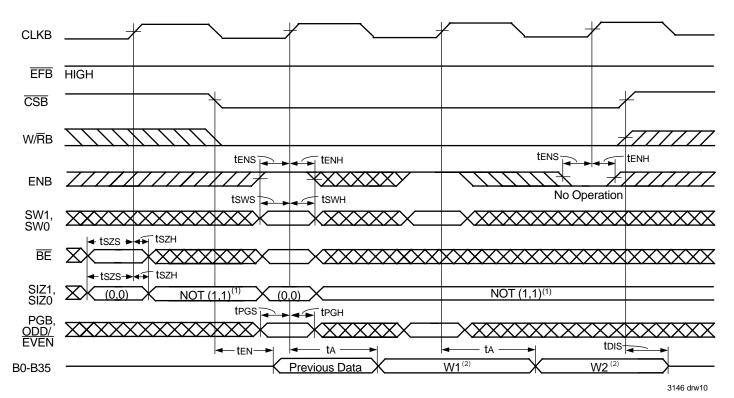

#### **BUS-MATCHING FIFO2 WRITES**

Data is written to the FIFO2 RAM in 36-bit long word increments. FIFO2 writes, with a long-word bus size, immediately store each long word in FIFO2 RAM. Data written to FIFO2 with a byte or word bus size stores the initial bytes or words in auxiliary registers. The CLKB rising edge that writes the fourth byte or the second word of long word to FIFO2 also stores the entire long word in FIFO2 RAM. The bytes are arranged in the manner shown in Figure 2.

Each FIFO2 write with a new bus-size implementation resets the state machine that controls the data flow from the auxiliary registers to the FIFO2 RAM. Therefore, implementing a new bus size and performing a FIFO2 write before bytes or words stored in the auxiliary registers have been loaded to FIFO2 RAM results in a loss of data.

#### PORT-B MAIL REGISTER ACCESS

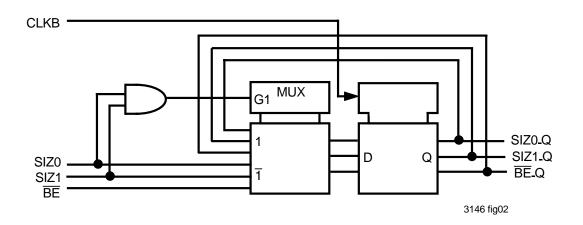

In addition to selecting port-B bus sizes for FIFO reads and writes, the port B bus Size select (SIZ0, SIZ1) inputs also access the mail registers. When both SIZ0 and SIZ1 are HIGH, the mail1 register is accessed for a port B long word read and the mail2 register is accessed for a port B long word write. The mail register is accessed immediately and any bus-sizing operation that may be underway is unaffected by the mail register access. After the mail register access is complete, the previous FIFO access can resume in the next CLKB cycle. The logic diagram in Figure 3 shows the previous bus-size selection is preserved when the mail registers are accessed from port B. A port B bus size is implemented on each rising CLKB edge according to the states of SIZ0\_Q, SIZ1\_Q, and  $\overline{BE}_Q$ .

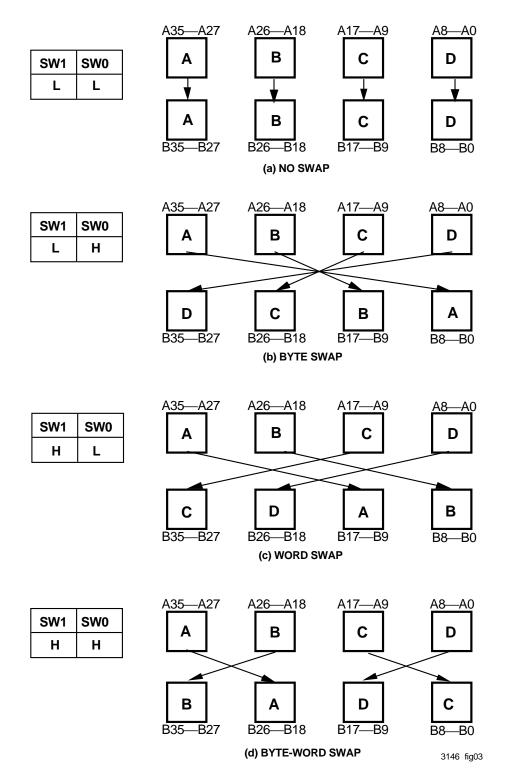

#### **BYTE SWAPPING**

The byte-order arrangement of data read from FIFO1 or data written to FIFO2 can be changed synchronous to the rising edge of CLKB. Byte-order swapping is not available for mail register data. Four modes of byte-order swapping (including no swap) can be done with any data port size selection. The order of the bytes are rearranged within the long word, but the bit order within the bytes remains constant.

Byte arrangement is chosen by the port B Swap select (SW0, SW1) inputs on a CLKB rising edge that reads a new long word from FIFO1 or writes a new long word to FIFO2. The byte order chosen on the first byte or first word of a new long word read from FIFO1 or written to FIFO2 is maintained until the entire long word is transferred, regardless of the SW0 and SW1 states during subsequent writes or reads. Figure 4 is an example of the byte-order swapping available for long words. Performing a byte swap and bus size simultaneously for a FIFO1 read first rearranges the bytes as shown in Figure 4, then outputs the bytes as shown in Figure 2. Simultaneous bus-sizing and byte-swapping operations for FIFO2 writes, first loads the data according to Figure 2, then swaps the bytes as shown in Figure 4 when the long word is loaded to FIFO2 RAM.

Figure 2. Dynamic Bus Sizing

#### **PARITY CHECKING**

The port A inputs (A0-A35) and port B inputs (B0-B35) each have four parity trees to check the parity of incoming (or outgoing) data. A parity failure on one or more bytes of the port A data bus is reported by a LOW level on the port Parity Error Flag (PEFA). A parity failure on one or more bytes of the port B data input that are valid for the bus-size implementation is reported by a LOW level on the port B Parity Error Flag (PEFB). Odd or Even parity checking can be selected, and the Parity Error Flags can be ignored if this feature is not desired.

Parity status is checked on each input bus according to the level of the Odd/Even parity (ODD/EVEN) select input. A parity error on one or more valid bytes of a port is reported by a LOW level on the corresponding port Parity Error Flag (PEFA, PEFB) output. Port A bytes are arranged as A0-A8, A9-A17, A18-A26, and A27-A35. Port B bytes are arranged as B0-B8, B9-B17, B18-B26, and B27-B35, and its valid bytes are those used in a port B bus-size implementation. When Odd/Even parity is selected, a port Parity Error Flag (PEFA, PEFB) is LOW if any byte on the port has an odd/even number of LOW levels applied to the bits.

The four parity trees used to check the A0-A35 inputs are shared by the mail2 register when parity generation is selected for port A reads (PGA = HIGH). When a port A read from the mail2 register with parity generation is selected with CSA LOW, ENA HIGH, W/RA LOW, MBA HIGH, and PGA HIGH, the port A Parity Error Flag (PEFA) is held HIGH regardless of the levels applied to the A0-A35 inputs. Likewise, the parity trees used to check the B0-B35 inputs are shared by the mail1 register when parity generation is selected for port B reads (PGB = HIGH). When a port B read from the mail1 register with parity generation is selected for port B reads (PGB = HIGH). When a port B read from the mail1 register with parity generation is selected with CSB LOW, ENB HIGH, W/RB LOW, both SIZ0 and SIZ1 HIGH, and PGB HIGH, the port B Parity Error Flag (PEFB) is held HIGH regardless of the levels applied to the B0-B35 inputs.

#### PARITY GENERATION

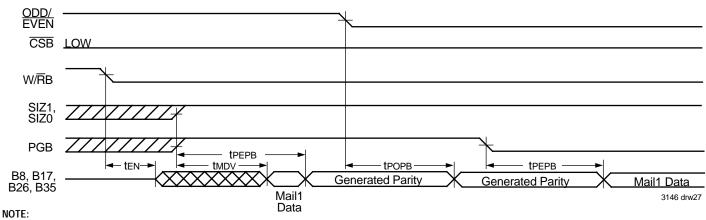

A HIGH level on the port A Parity Generate select (PGA) or port B Parity Generate select (PGB) enables the IDT723614 to generate parity bits for port reads from a FIFO or mailbox register. Port A bytes are arranged as A0-A8, A9-A17, A18-26, and A27-A35, with the most significant bit of each byte used as the parity bit. Port B bytes are arranged as B0-B8, B9-B17, B18-B26, and B27-B35, with the most significant bit of each byte used as the parity bit. A write to a FIFO or mail register stores the levels applied to all nine inputs of a byte regardless of the state of the Parity Generate select (PGA, PGB) inputs. When data is read from a port with parity generation selected, the lower eight bits of each byte are used to generate a parity bit according to the level on the ODD/ EVEN select. The generated parity bits are substituted for the levels originally written to the most significant bits of each byte as the word is read to the data outputs.

Parity bits for FIFO data are generated after the data is read from SRAM and before the data is written to the output register. Therefore, the port A Parity Generate select (PGA) and Odd/Even parity select (ODD/EVEN) have setup and hold time constraints to the port A Clock (CLKA) and the port B Parity Generate select (PGB) and ODD/EVEN have setup and hold-time constraints to the port B Clock (CLKB). These timing constraints only apply for a rising clock edge used to read a new long word to the FIFO output register.

The circuit used to generate parity for the mail1 data is shared by the port B bus (B0-B35) to check parity and the circuit used to generate parity for the mail2 data is shared by the port A bus (A0-A35) to check parity. The shared parity trees of a port are used to generate parity bits for the data in a mail register when the port Chip Select ( $\overline{CSA}$ ,  $\overline{CSB}$ ) is LOW, Enable (ENA, ENB) is HIGH, Write/ Read select ( $W/\overline{RA}$ ,  $W/\overline{RB}$ ) input is LOW, the Mail register is selected (MBA is HIGH for port A; both SIZ0 and SIZ1 are HIGH for port B), and port Parity Generate select (PGA, PGB) is HIGH. Generating parity for mail register data does not change the contents of the register.

Figure 3. Logic Diagrams for SIZ0, SIZ1, and BE Register

Figure 4. Byte Swapping (Long Word Size Example)

Figure 5. Device Reset Loading the X Register with the Value of Eight

NOTE:

1. Written to FIFO1.

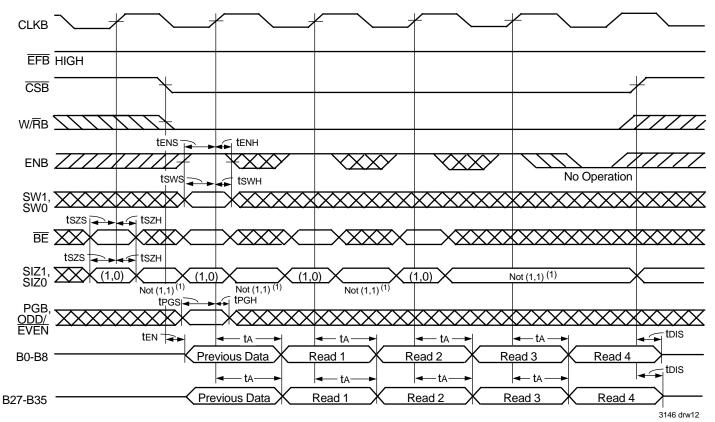

Figure 6. Port-A Write Cycle Timing for FIF01

NOTE:

1. SIZ0 = HIGH and SIZ1 = HIGH writes data to the mail2 register

# DATA SWAP TABLE FOR LONG-WORD WRITES TO FIF02

| SWAP M | ODE |                            | DATA WRITT | en to fifo2 |         | DATA READ FROM FIFO2 |       |   |   |  |

|--------|-----|----------------------------|------------|-------------|---------|----------------------|-------|---|---|--|

| SW1    | SW0 | B35-27 B26-18 B17-B9 B8-B0 |            | A35-27      | A26-A18 | A17-A9               | A8-A0 |   |   |  |

| L      | L   | А                          | В          | С           | D       | А                    | В     | С | D |  |

| L      | Н   | D                          | С          | В           | А       | А                    | В     | С | D |  |

| Н      | L   | С                          | D          | А           | В       | А                    | В     | С | D |  |

| Н      | Н   | В                          | А          | D           | С       | А                    | В     | С | D |  |

NOTES:

1. SIZ0 = HIGH and SIZ1 = HIGH writes data to the mail2 register.

2. PEFB indicates parity error for the following bytes: B35-B27 and B26-B18 for Big-Endian bus, and B17-B9 and B8-B0 for Little-Endian bus.

# DATA SWAP TABLE FOR WORD WRITES TO FIF02

| SN   | /AP | WRITE | -          | data w | RITTEN TO FIF | 02    |                      |         |        |       |  |

|------|-----|-------|------------|--------|---------------|-------|----------------------|---------|--------|-------|--|

| MODE |     | NO.   | BIG-ENDIAN |        | LITTLE-ENDIAN |       | DATA READ FROM FIFO2 |         |        |       |  |

| SW1  | SW0 |       | B35-27     | B26-18 | B17-B9        | B8-B0 | A35-27               | A26-A18 | A17-A9 | A8-A0 |  |

| L    | L   | 1     | А          | В      | С             | D     | A                    | В       | С      | D     |  |

|      |     | 2     | С          | D      | A             | В     |                      |         |        |       |  |

| L    | Н   | 1     | D          | С      | В             | А     | А                    | В       | С      | D     |  |

|      |     | 2     | В          | А      | D             | С     |                      |         |        |       |  |

| Н    | L   | 1     | С          | D      | A             | В     | A                    | В       | С      | D     |  |

|      |     | 2     | А          | В      | С             | D     |                      |         |        |       |  |

| Н    | Н   | 1     | В          | A      | D             | С     | A                    | В       | С      | D     |  |

|      |     | 2     | D          | С      | В             | А     |                      |         |        |       |  |

Figure 8. Port-B Word Write Cycle Timing for FIFO2

#### NOTES:

1. SIZ0 = HIGH and SIZ1 = HIGH writes data to the mail2 register.

2. PEFB indicates parity error for the following bytes: B35—B27 for Big-Endian bus and B17—B9 for Little-Endian bus.

# DATA SWAP TABLE FOR BYTE WRITES TO FIFO2

| SW  | SWAP<br>MODE |                  | DATA W                   | RITTEN TO FIFO2  | DATA READ FROM FIF02 |         |        |       |  |

|-----|--------------|------------------|--------------------------|------------------|----------------------|---------|--------|-------|--|

|     |              |                  | BIG-ENDIAN LITTLE-ENDIAN |                  |                      |         |        |       |  |

| SW1 | SW0          |                  | B35-27 B8-B0             |                  | A35-27               | A26-A18 | A17-A9 | A8-A0 |  |

| L   | L            | 1<br>2<br>3<br>4 | A<br>B<br>C<br>D         | D<br>C<br>B<br>A | A                    | В       | с      | D     |  |

| L   | н            | 1<br>2<br>3<br>4 | D<br>C<br>B<br>A         | A<br>B<br>C<br>D | A                    | В       | С      | D     |  |

| н   | L            | 1<br>2<br>3<br>4 | C<br>D<br>A<br>B         | B<br>A<br>D<br>C | A                    | В       | С      | D     |  |

| н   | н            | 1<br>2<br>3<br>4 | B<br>A<br>D<br>C         | C<br>D<br>A<br>B | A                    | В       | С      | D     |  |

Figure 9. Port-B Byte Write Cycle Timing for FIFO2

NOTES:

1. SIZ0 = HIGH and SIZ1 = HIGH selects the mail1 register for output on B0-B35.

2. Data read from FIFO1.

# DATA SWAP TABLE FOR FIFO LONG-WORD READS FROM FIFO1

|        | DATA WRI | TTEN TO FIF | 01    | SWAP    | MODE | DATA READ FROM FIF01 |        |        |       |  |

|--------|----------|-------------|-------|---------|------|----------------------|--------|--------|-------|--|

| A35-27 | A26-A18  | A17-A9      | A8-A0 | SW1 SW0 |      | B35-27               | B26-18 | B17-B9 | B8-B0 |  |

| А      | В        | С           | D     | L       | L    | А                    | В      | С      | D     |  |

| А      | В        | С           | D     | L       | Н    | D                    | С      | В      | А     |  |

| А      | В        | С           | D     | Н       | L    | С                    | D      | А      | В     |  |

| Α      | В        | С           | D     | Н       | Н    | В                    | А      | D      | С     |  |

Figure 10. Port-B Long-Word Read Cycle Timing for FIFO1

#### NOTES:

1. SIZ0 = HIGH and SIZ1 = HIGH selects the mail1 register for output on B0-B35.

2. Unused word B0-B17 or B18-B35 holds last FIFO1 output register data for word-size reads.

# DATA SWAP TABLE FOR WORD READS FROM FIF01

|         |                       |        |       |           |     |             |            | DATA REAL | D FROM FIFO   | 1      |

|---------|-----------------------|--------|-------|-----------|-----|-------------|------------|-----------|---------------|--------|

|         | DATA WRITTEN TO FIFO1 |        |       | SWAP MODE |     | READ<br>NO. | BIG-ENDIAN |           | LITTLE-ENDIAN |        |

| A35-A27 | A26-A18               | A17-A9 | A8-A0 | SW1       | SW0 |             | B35-B27    | B26-B18   | B17-B9        | B8-B0  |

| A       | В                     | С      | D     | L         | L   | 1<br>2      | A<br>C     | B<br>D    | C<br>A        | D<br>B |

| A       | В                     | С      | D     | L         | Н   | 1<br>2      | D<br>B     | C<br>A    | B<br>D        | A<br>C |

| A       | В                     | С      | D     | Н         | L   | 1<br>2      | C<br>A     | D<br>B    | A<br>C        | B<br>D |

| А       | В                     | С      | D     | Н         | Н   | 1<br>2      | B<br>D     | A<br>C    | D<br>B        | C<br>A |

Figure 11. Port-B Word Read Cycle Timing for FIFO1

#### NOTES:

1. SIZ0 = HIGH and SIZ1 = HIGH selects the mail1 register for output on B0-B35.

2. Unused bytes hold last FIFO1 output register data for byte-size reads.

# DATA SWAP TABLE FOR BYTE READS FROM FIF01

|         |          |                |       |      |       |                  | DATA READ FROM FIFO 1 |                   |  |

|---------|----------|----------------|-------|------|-------|------------------|-----------------------|-------------------|--|

|         | data wri | TTEN TO FIFO 1 | l     | SWAF | PMODE | READ<br>NO.      | BIG-<br>Endian        | LITTLE-<br>Endian |  |

| A35-A27 | A26-A18  | A17-A9         | A8-A0 | SW1  | SW0   |                  | B35-B27               | B8-B0             |  |

| A       | В        | С              | D     | L    | L     | 1<br>2<br>3<br>4 | A<br>B<br>C<br>D      | D<br>C<br>B<br>A  |  |

| А       | В        | С              | D     | L    | н     | 1<br>2<br>3<br>4 | D<br>C<br>B<br>A      | A<br>B<br>C<br>D  |  |

| A       | В        | С              | D     | Н    | L     | 1<br>2<br>3<br>4 | C<br>D<br>A<br>B      | B<br>A<br>D<br>C  |  |

| А       | В        | С              | D     | Н    | Н     | 1<br>2<br>3<br>4 | B<br>A<br>D<br>C      | C<br>D<br>A<br>B  |  |

Figure 12. Port-B Byte Read Cycle Timing for FIFO1

#### NOTES:

1. tskew1 is the minimum time between a rising CLKA edge and a rising CLKB edge for EFB to transition HIGH in the next CLKB cycle. If the time between the rising CLKA edge and rising CLKB edge is less than tskew1, then the transition of EFB HIGH may occur one CLKB cycle later than shown.

2. Port-B size of long word is selected for FIFO1 read by SIZ1 = LOW, SIZ0 = LOW. If port-B size is word or byte, EFB is set LOW by the last word or byte read from FIFO1, respectively.

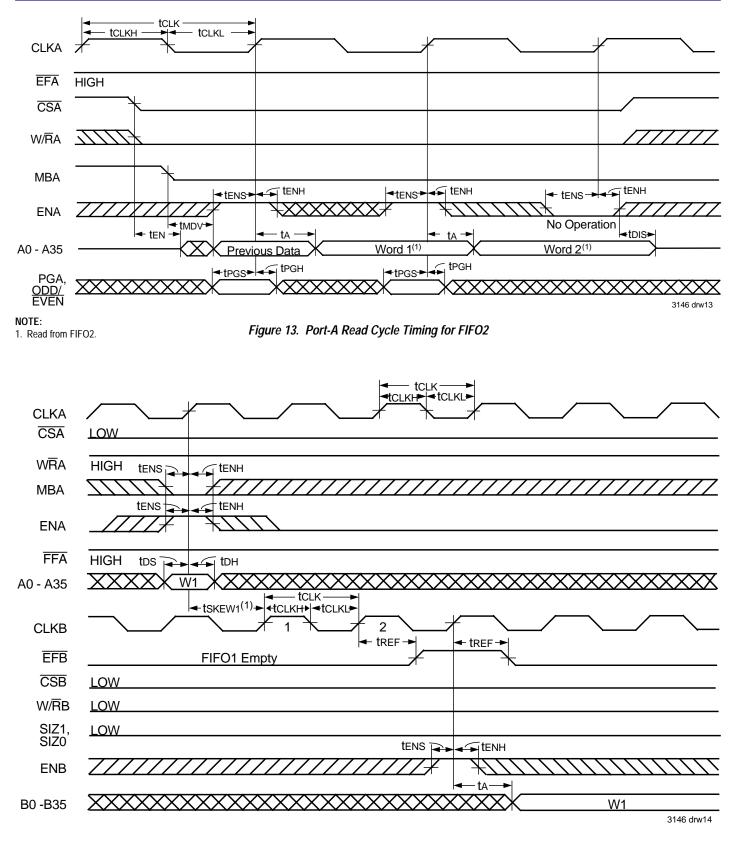

#### Figure 14. **EFB** Flag Timing and First Data Read when FIFO1 is Empty

#### NOTES:

1. tskew1 is the minimum time between a rising CLKB edge and a rising CLKA edge for EFA to transition HIGH in the next CLKA cycle. If the time between the rising CLKB edge and rising CLKA edge is less than tskew1, then the transition of EFA HIGH may occur one CLKA cycle later than shown.

2. Port B size of long word is selected for FIFO2 write by SIZ1 = LOW, SIZ0 = LOW. If port B size is word or byte tskew1 is referenced to the rising CLKB edge that writes the last word or byte of the long word, respectively.

### Figure 15. EFA Flag Timing and First Data Read when FIFO2 is Empty

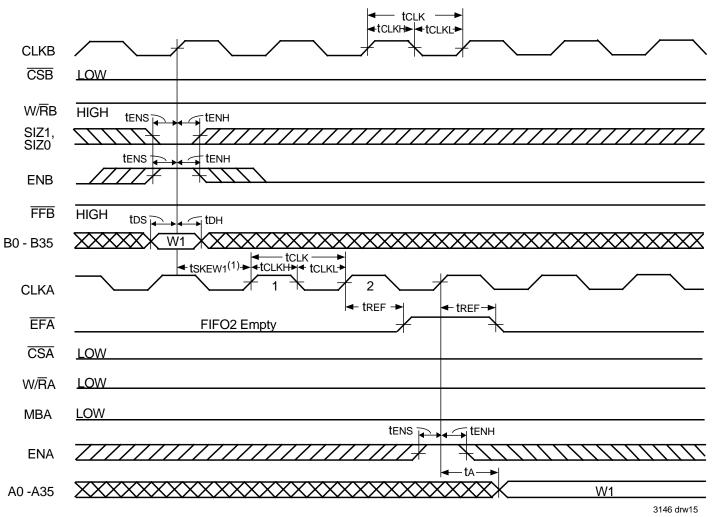

#### NOTES:

1. tskewi is the minimum time between a rising CLKB edge and a rising CLKA edge for FFA to transition HIGH in the next CLKA cycle. If the time between the rising CLKB edge and rising CLKA edge is less than tskewi, then FFA may transition HIGH one CLKA cycle later than shown.

2. Port B size of long word is selected for FIFO1 read by SIZ1 = LOW, SIZ0 = LOW. If port B size is word or byte, tskew1 is referenced from the rising CLKB edge that reads the last word or byte of the long word, respectively.

Figure 16. FFA Flag Timing and First Available Write when FIFO1 is Full.

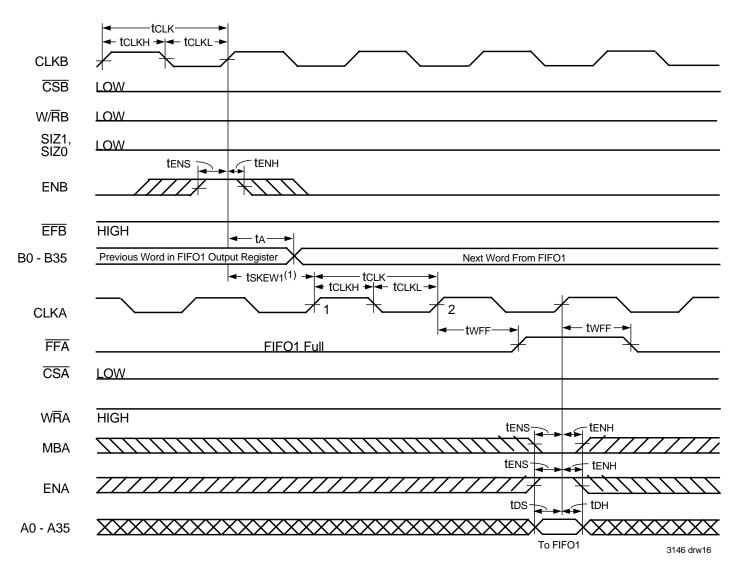

NOTES:

1. tskew1 is the minimum time between a rising CLKA edge and a rising CLKB edge for FFB to transition HIGH in the next CLKB cycle. If the time between the rising CLKA edge and rising CLKB edge is less than tskew1, then FFB may transition HIGH one CLKB cycle later than shown.

2. Port B size of long word is selected for FIFO2 write by SIZ1 = LOW, SIZ0 = LOW. If port B size is word or byte, FFB is set LOW by the last word or byte write of the long word, respectively.

NOTES:

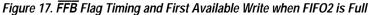

1. tskEw2 is the minimum time between a rising CLKA edge and a rising CLKB edge for  $\overline{AEB}$  to transition HIGH in the next CLKB cycle. If the time between the rising CLKA edge and rising CLKB edge is less than tskEw2, then  $\overline{AEB}$  may transition HIGH one CLKB cycle later than shown.

2. FIFO1 Write (CSA = LOW, W/RA = HIGH, MBA = LOW), FIFO1 read (CSB = LOW, W/RB = LOW, MBB = LOW).

3. Port B size of long word is selected for FIFO1 read by SIZ1 = LOW, SIZ0 = LOW. If port B size is word or byte, AEB is set LOW by the last word or byte read of the long word, respectively.

#### Figure 18. Timing for **AEB** when FIFO1 is Almost-Empty

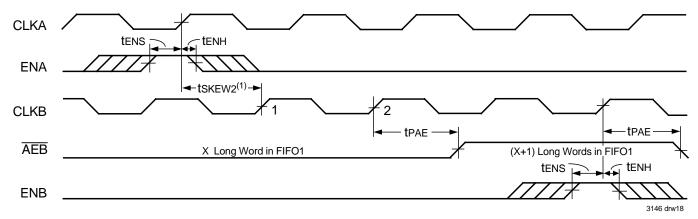

#### NOTES:

- 1. tskew2 is the minimum time between a rising CLKB edge and a rising CLKA edge for  $\overline{AEA}$  to transition HIGH in the next CLKA cycle. If the time between the rising CLKB edge and rising CLKA edge is less than tskew2, then  $\overline{AEA}$  may transition HIGH one CLKA cycle later than shown.

- 2. FIFO2 Write (CSB = LOW, W/RB = HIGH, MBB = LOW), FIFO2 read (CSA = LOW, W/RA = LOW, MBA = LOW).

- 3. Port B size of long word is selected for FIFO2 write by SIZ1 = LOW, SIZ0 = LOW. If port B size is word or byte, tskew2 is referenced from the rising CLKB edge that writes the last word or byte of the long word, respectively.

#### Figure 19. Timing for **AEA** when FIFO2 is Almost-Empty

#### NOTES:

- 1. tskew2 is the minimum time between a rising CLKA edge and a rising CLKB edge for  $\overline{AFA}$  to transition HIGH in the next CLKA cycle. If the time between the rising CLKA edge and rising CLKB edge is less than tskew2, then  $\overline{AFA}$  may transition HIGH one CLKB cycle later than shown.

- 2. FIFO1 Write (CSA = LOW, W/RA = HIGH, MBA = LOW), FIFO1 read (CSB = LOW, W/RB = LOW, MBB = LOW).

- 3. Port B size of long word is selected for FIFO1 read by SIZ1 = LOW, SIZ0 = LOW. If port B size is word or byte, tskew2 is referenced from the last word or byte read of the long word, respectively.

#### Figure 20. Timing for AFA when FIFO1 is Almost-Full

#### NOTES:

- 1. tskew2 is the minimum time between a rising CLKB edge and a rising CLKA edge for AFB to transition HIGH in the next CLKB cycle. If the time between the rising CLKB edge and rising CLKA edge is less than tskew2, then AFB may transition HIGH\_one CLKA cycle later than shown.

- 2. FIFO2 Write (CSB = LOW, W/RB = HIGH, MBB = LOW), FIFO2 read (CSA = LOW, W/RA = LOW, MBA = LOW).

- 3. Port B size of long word is selected for FIFO2 write by SIZ1 = LOW, SIZ0 = LOW. If port B size is word or byte, AFB is set LOW by the last word or byte read of the long word, respectively.

#### Figure 21. Timing for AFB when FIFO2 is Almost-Full

NOTE:

<sup>1.</sup> Port B Parity Generation off (PGB = LOW).

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

#### NOTE:

1. Port-A Parity Generation off (PGA = LOW).

# Figure 24. ODD/EVEN. W/RA, MBA, and PGA to PEFA Timing

Figure 25. ODD/EVEN. W/RB, SIZ1, SIZ0, and PGB to PEFB Timing

### NOTE:

Figure 26. Parity Generation Timing when Reading from the Mail2 Register

NOTE:

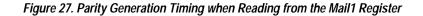

1. Includes probe and jig capacitance.

# **ORDERING INFORMATION**

NOTE:

1. Industrial temperature range product for 20ns speed grade is available as a standard device. All other speed grades are available by special order.

### **DATASHEET DOCUMENT HISTORY**

03/05/2002 pgs. 1, 8, 9 and 32.

*CORPORATE HEADQUARTERS* 2975 Stender Way Santa Clara, CA 95054 *for SALES:* 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com for TECH SUPPORT: e-mail: FIFOhelp@idt.com Phone: (408) 330-1753